Современная разработка и серийное производство микроконтроллеров AVR требует не только высокого уровня программной и аппаратной совместимости, но и надежного тестирования в условиях нестандартной синхронизации питающей сети. В условиях реального мира частоты сети питания могут дрейфовать, присутствовать гармоники, импульсные помехи и периодические выбросы. Именно поэтому суперпоследовательное тестирование AVR микроконтроллеров на частотах с нестандартной синхронизацией сети питания становится одним из ключевых инструментов обеспечения надежности, воспроизводимости и долговечности проектов — от бытовой электроники до промышленных систем и интернета вещей. Эта статья рассматривает методологию, практические подходы, аппаратные средства и программные техники, используемые для проведения такого тестирования.

- Что такое нестандартная синхронизация сети питания и почему она влияет на AVR

- Стратегия суперпоследовательного тестирования

- Выбор диапазона и шага частот питания

- Аппаратная схема тестирования

- Программная архитектура и методики измерения

- Методы оценки точности времени и прерываний

- Метрики качества и критерии прохождения

- Практические сценарии тестирования AVR

- Сценарий А: тестирование таймингов периферии в условиях дрейфа частоты

- Сценарий Б: влияние гармоник и пульсаций на работу АЦП и PWM

- Сценарий В: тестирование минимального устойчивого тока и перегрева

- Инструменты и методы мониторинга

- Построение отчетности и анализ данных

- Безопасность и отказоустойчивость

- Заключение

- Что такое «суперпоследовательное» тестирование и как оно применяется к AVR на нестандартной синхронизации питания?

- Какие методы калибровки и мониторинга частоты и фазы питания лучше всего подходят для AVR при нестандартной синхронизации?

- Какие конкретные сценарии тестирования на нестандартной синхронизации питания стоит включить в план?

- Как автоматизировать процедуру тестирования и сохранять репозитории результатов для повторяемости?

Что такое нестандартная синхронизация сети питания и почему она влияет на AVR

Нестандартная синхронизация сети питания относится к ситуациям, когда частота или форма питающей сети отличается от идеального синуса 50 Гц (или 60 Гц в зависимости от региона), может иметь дрейф частоты, модуляцию, гармоники и скачкообразные переходы. В микроконтроллерах AVR тактовая генерация является критическим параметром: такты ядра и периферии определяют точность временных последовательностей, таймингов SPI/I2C/UART, ШИМ, АЦП, АЦП-цикл, DDS-генераторы, задержки и прерывности. Недостаточная синхронизация между тактовой сетью и питающей сетью приводит к ошибкам тайминга, дребезгу прерываний, неверному функционалу алгоритмов, ошибкам в ШИМ-управлении моторами и в критических регуляторах.

Кроме того, нестандартная синхронизация влияет на энергопотребление и тепловые режимы. При изменяющейся частоте сети изменяется стабильность питания, что может приводить к дрейнованию стабильности тактового генератора, особенно у бюджетных кварцевых резонаторов или RC-генераторов. В условиях нестабильной сети микроконтроллер может переходить в режимы пониженного потребления с непредсказуемыми частотными дрейфами, что разрушает реальное поведение систем в длительной эксплуатации. Именно поэтому необходима серия тестов, охватывающих широкий диапазон частот и форм питающего сигнала, чтобы оценить устойчивость работы AVR.

Стратегия суперпоследовательного тестирования

Суть суперпоследовательного тестирования состоит в создании контролируемой набора условий, которые последовательно моделируют экстремальные и типичные сценарии сетевой энергетики. Такой подход позволяет получить репрезентативные данные о поведении MCU в реальных условиях и выявить скрытые дефекты на ранних стадиях разработки. Ниже приведены ключевые принципы стратегии:

- Разбиение диапазона частот питания на интервалы с высокой степенью детализации near-critical точек: дрейф частоты, гармоники, пульсации и переходные процессы.

- Изоляция влияния сетевых параметров на тактовую генерацию AVR через независимую настройку генераторов тактов, источников питания и схемы фильтрации.

- Повторяемость условий тестирования для статистической верификации устойчивости и воспроизводимости ошибок.

- Комбинирование аппаратного стресс-теста с программными сценариями, которые проверяют критические алгоритмы: прерывания, тайминги, коммутация периферии, генерация сигнальных волн.

- Систематическая регистрация параметров и параметрический анализ по всем тестовым сценариям: частота, амплитуда, форма волны, температура, напряжение.

Выбор диапазона и шага частот питания

Важно охватить как экстремальные, так и реальные условия эксплуатации. Рекомендуется следующий подход:

- Начать с диапазона на 10–20% выше и ниже номинального значения сети. Например, для 50 Гц диапазон 40–60 Гц; для 60 Гц — 48–72 Гц, в зависимости от применяемой схемы питания и стабилизации тактовой частоты.

- Установить шаг тестирования на 0.5–2 Гц в окнах около критических точек и 5–20 Гц в диапазонах менее чувствительных зон. Более частые шаги — near-critical зоны, где возможны резонансные эффекты в схеме питания и тактовой генерации.

- Дополнительно включать редкие, но важные дергания частоты, такие как резкие скачки (например, на 5–10 Гц за доли секунды) для моделирования импульсных помех.

Аппаратная схема тестирования

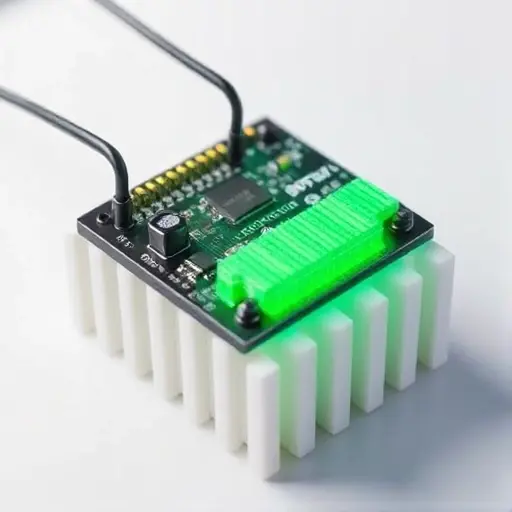

Ключевые элементы аппаратной части включают источник питания с регулируемым напряжением и частотой колебаний, синхронизированную с тестируемым предполагаемым сигналом AVR, устройство для изменения параметров сети и мониторинга состояния микроконтроллера. Основные компоненты:

- Регулируемые источники питания: способность генерировать стабильное напряжение, имитирующее реальное сетевое питание с вариациями по напряжению и частоте.

- Генератор синхронизационных сигналов: синхронизационный сигнал для AVR или программируемый тактовый генератор, который может эмулировать дрейф частоты центральной тактовой частоты.

- Фильтры питания и EMI/EMC защита: фильтры для подавления гармоник и пульсаций, обеспечивающие чистоту измерений.

- Средство измерения: осциллографы высокой скорости, логические анализаторы, измерители мощности и вольтамперные датчики для регистрации параметров питания и потребления MCU.

- Устройства стресс-теста: термостаты или источники нагрева, чтобы проверить влияние теплового дрейфа на стабильность тактового сигнала и периферии.

Важно обеспечить идентичность тестовой MCU в каждом запуске: одинаковые экземпляры, одинаковая версия прошивки, одинаковые параметры окружения. Это повышает репрезентативность и позволяет сравнивать результаты между тестированием разных партий или итераций разработки.

Программная архитектура и методики измерения

Программное обеспечение должно эффективно управлять конфигурациями теста и регистрировать результаты. Основные принципы:

- Независимая калибровка тактовой частоты: проверка точности частоты системного тактового генератора (CLK) и периферийных таймеров относительно внешнего источника питания.

- Измерение ошибок по времени: использование аппаратной поддержки микроконтроллера для точной измерения задержек между событиями, например, с использованием счетчика событий (cycle counter) или внешних триггеров.

- Проверка критических переферий: UART, SPI, I2C, ADC, PWM, таймера прерываний — тестирование с различной частотой питания, чтобы выявить устойчивость функций во всех режимах.

- Логирование и анализ: сбор статистики по каждому сценарию (среднее, дисперсия, максимум, минимум), а также визуализация временных рядов и зависимостей между параметрами питания и поведением MCU.

- Автоматизация повторяющихся сценариев: скрипты на языке, поддерживаемом инструментами тестирования, обеспечивающие повторяемость и воспроизводимость.

Методы оценки точности времени и прерываний

Основные техники включают:

- Сравнение времени выполнения критических функций с эталонными профилями, полученными при стабильной частоте питания.

- Проверка устойчивости прерываний при дрейфе частоты и гармониках, анализ задержек между событием и обработчиком.

- Испытания на скольжение тактов: мониторинг шагов дрейфа и их влияние на периодичность генераций PWM/ADC-цикла.

Метрики качества и критерии прохождения

Для оценки результатов применяются следующие метрики:

- Ошибки тайминга: количество случаев, когда период или длительность сигнала выходит за допустимый диапазон.

- Дрейф частоты: средний и максимальный дрейф относительно номинала за заданный интервал времени.

- Погрешность периферии: отклонения в скорости передачи по UART/SPI/I2C, изменение величины ШИМ и АЦП-значений.

- Энергетическая стабильность: вариации потребления и тепловой дрейф, влияющие на устойчивость питания MCU.

Практические сценарии тестирования AVR

Ниже перечислены типичные сценарии, которые часто применяются для оценки устойчивости AVR под нестандартной синхронизацией питания.

Сценарий А: тестирование таймингов периферии в условиях дрейфа частоты

Цель: проверить устойчивость таймингов SPI/I2C/UART и задержек прерываний под различными условиями питания. Выполнение:

- Установить базовую частоту тактовой генерации и зафиксировать параметры питания.

- Последовательно увеличивать/уменьшать частоту питания в заданном диапазоне.

- Выполнить серию операций обмена данными и измерить отклонения по времени и потокам.

Сценарий Б: влияние гармоник и пульсаций на работу АЦП и PWM

Цель: оценить искажения в АЦП и регулируемых сигналах PWM под воздействием сетевых помех. Выполнение:

- Имитировать гармоники и пульсацию через соответствующие модуляторы и фильтры питания.

- Параллельно запускать задачи, использующие АЦП и PWM, и фиксировать вариации выходных уровней и частот.

Сценарий В: тестирование минимального устойчивого тока и перегрева

Цель: проверить, как изменение температуры и напряжения влияет на стабильность тактового генератора и потребление MCU. Выполнение:

- Включить тепловой стресс и измерять параметры питания и частоту до/после превышения порогов.

- Проводить длительные тесты на стабилизацию потребления и симптомов деградации периферии.

Инструменты и методы мониторинга

Эффективное суперпоследовательное тестирование требует комплексного набора инструментов.

- Осциллографы с высокой скоростью выборки и доступом к аналоговым цепям питания для измерения формы сигнала и гармоник.

- Логические анализаторы для регистрации последовательностей на шинах и совместимости сигналов между MCU и внешними устройствами.

- Измерители мощности и вольтамперные датчики для регистрации потребления и зависимости от частоты питания.

- Тепловизионные камеры или термостаты для контроля температуры и выявления локальных перегревов.

- Эмуляторы и программаторы AVR для быстрого переноса прошивок и повторного тестирования.

Построение отчетности и анализ данных

Ключ к принятию решений — систематизация результатов. Рекомендуется следующий подход к отчетности:

- Структурирование данных по сценариям, диапазонам частот и параметрам окружающей среды.

- Графическое представление зависимостей: частота питания vs. дрейф частоты, ошибки тайминга, потребление и температура.

- Статистический анализ: расчёт доверительных интервалов, дисперсии и корреляций между параметрами.

- Сводный рейтинг устойчивости по каждому устройству и по прошивке, чтобы определить области для улучшения.

Безопасность и отказоустойчивость

Работа в условиях нестандартной синхронизации сети требует особого внимания к безопасности и защите оборудования.

- Управление нагревом и перегревом: предусматривайте защиту от перегрева микроконтроллера и цепей питания.

- Избыточность и резервирование: применение резервных источников питания и дублирующих схем для проверки на случай отказа одного источника.

- Защита от импульсных помех: соответствующие фильтры, экраны и коррозионная защита кабелей.

- Документация и аудит: запись всех конфликтных сценариев, изменений в конфигурации и версий прошивок для аудита и повторяемости экспериментов.

Заключение

Суперпоследовательное тестирование AVR микроконтроллеров на частотах с нестандартной синхронизацией сети питания является необходимым элементом инженерной практики в условиях современной электроники. Оно позволяет заранее выявлять слабые места в таймингах, устойчивости периферийных устройств и энергопотреблении, обеспечивая высокую надёжность устройств в реальном мире. Комплексный подход, включающий детальную методологию, грамотный выбор диапазонов частот, продуманную аппаратную и программную архитектуру, а также систематическую обработку данных и безопасные схемы эксплуатации — все это приводит к более качественным продуктам и снижению рисков в серийном производстве. В условиях роста требований к точности и долговечности электронных систем, подобные тесты становятся не просто хорошей практикой, а необходимостью для конкурентоспособного и безопасного решения.

Что такое «суперпоследовательное» тестирование и как оно применяется к AVR на нестандартной синхронизации питания?

Суперпоследовательное тестирование — это подход, когда тесты выполняются в строгой последовательности с контролируемыми переходами по всем параметрам, чтобы отслеживать влияние каждого изменения на поведение микроконтроллера. При нестандартной синхронизации сети питания это означает одновременную проверку работы ядра, периферийных модулей и таймингов при разных частотах питания, стартовых спадах и изменениях формы сигнала питания. Практически это позволяет выявлять проблемы с тактовой частотой, задержками входных и выходных сигналов, устойчивостью к помехам и кросс-модуляционными эффектами, которые возникают именно при несоответствии или нестандартности синхронизации с сетью питания.

Какие методы калибровки и мониторинга частоты и фазы питания лучше всего подходят для AVR при нестандартной синхронизации?

Полезно сочетать аппаратные и программные методы: использование линейного источника питания с регулируемой частотой импульсов, измерение реального Vcc и всех ключевых узлах с помощью ADC микроконтроллера и внешних тестовых стендов. Включите мониторинг линий питания (Vcc, Vin, Vref), измерение дрейфа частоты тактового генератора(MCU) при изменении входного напряжения, анализ ошибок по шине UART/SPI/I2C и тесты на устойчивость к кратковременным просадкам напряжения. Автоматизируйте сбор результатов и расчёт метрик: процент ошибок, среднее отклонение частоты, длительности задержек, критические пороги для конкретного семейства AVR.

Какие конкретные сценарии тестирования на нестандартной синхронизации питания стоит включить в план?

1) Резкое увеличение/уменьшение Vcc в диапазоне допустимых величин с фиксацией частоты тактирования; 2) Изменение формы питания (пульсации, ripple) и тестирование устойчивости к EMI/EMC изза сетевых помех; 3) Проверка корректности работы таймеров, счётчиков и прерываний при различных фазах и задержках синхронизации; 4) Тест GPIO-переключений и PWM при нестандартной фазе питания; 5) Тестирование программного профиля обновления Flash/EEPROM и кросс-сопряжения с энергоснабжением в условиях нестандартной синхронизации.

Как автоматизировать процедуру тестирования и сохранять репозитории результатов для повторяемости?

Используйте последовательность тестов в CI-пайплайне или локальном тестовом стенде с управлением через скрипты (Python/Lua) и аппаратные интерфейсы (JTAG/SWD, UART, I2C). Важны: фиксированные профили питания, версионирование тест-кейсов, хранение результатов в формате CSV/JSON и генерация отчетов с графиками частот, ошибок и задержек. Автоматический ретрай и пороговые уведомления по аномалиям помогают обеспечить повторяемость и ускорить регрессию по мере изменения дизайна или условий питания.